中國粉體網訊 在半導體產業的發展歷程中,摩爾定律長期引領著芯片性能的提升與規模的擴張。然而,隨著晶體管尺寸不斷逼近物理極限,量子隧穿效應等問題日益凸顯,傳統技術路徑遭遇瓶頸。玻璃通孔(TGV)技術憑借獨特優勢,或成為半導體突破摩爾定律束縛、開啟新增長曲線的關鍵力量。

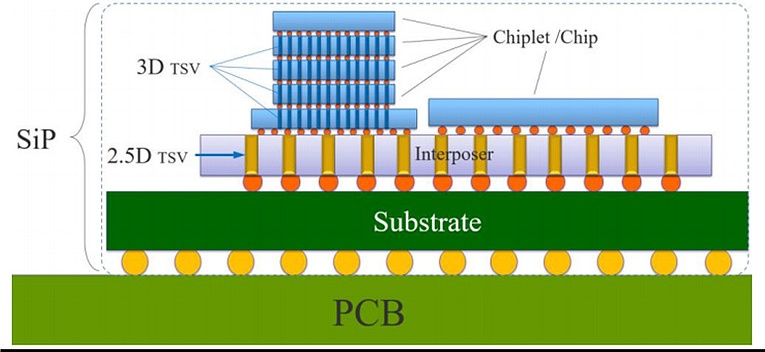

2.5D/3D封裝工藝中的TSV技術

我們都知道,要實現芯片性能的提升就需要堆疊更多的晶體管,根據“摩爾定律”,芯片上容納的晶體管數目每18到24個月增加一倍。過去數十年,伴隨“摩爾定律”推進,單位面積晶體管密度持續攀升,驅動芯片不斷向微型化演進,催生出智能手機、筆記本電腦等一系列便攜式電子產品,深刻重塑了大眾的生活與消費形態。

但“摩爾定律”終有觸及天花板的一天。當晶圓制造工藝演進到14nm、7nm、5nm,直至當下最前沿的3nm,其有效性愈發受到嚴峻挑戰:工藝推進舉步維艱,性能提升陷入瓶頸,成本卻如脫韁野馬般大幅飆升。

近兩年來,AI浪潮席卷全球,AI服務器對算力的需求呈井噴式爆發。強大算力的背后固然需要強勁芯片支撐,但提升芯片性能是否只能依賴光刻工藝的持續突破?答案是否定的。當前芯片已高度微型化,且服務器對輕薄化的要求遠低于消費電子,一條全新思路應運而生——通過堆疊多顆芯片實現算力躍升。打個不是很形象的比喻就是一節火車頭不夠用那就多加兩節,猶如詹天佑當年的解決思路。

由此產生了問題,芯片堆疊如何實現?

目前先進封裝分為兩大類:一、基于XY平面延伸的先進封裝技術,主要通過重布線層工藝(RDL)進行信號的延伸和互連;二、基于Z軸延伸的先進封裝技術,主要是通過硅通孔(TSV)進行信號延伸和互連。顯然,芯片堆疊屬于第二種。通過TSV技術,可以將多個芯片進行垂直堆疊并互連。按照集成類型的不同分為2.5D TSV和3D TSV,2.5D TSV指的是位于硅轉接板上的TSV,3D TSV是指貫穿芯片體之中,連接上下層芯片的TSV。在3D TSV中,芯片相互靠近,所以延遲會更少,且互連長度縮短,能減少相關寄生效應,使器件以更高的頻率運行,從而轉化為性能改進,并更大程度的降低成本。TSV的尺寸范圍比較大,大的超過100um,小的小于1um。隨著工藝水平提升,TSV可以越做越小,密度越來越大。

基于TSV技術的系統級封裝 來源:萬聯證券研究所

TGV:TSV的升級

雖然在先進封裝領域TSV技術較為成熟,但其存在兩個主要問題。

成本高:材料上需高純度硅晶圓及特殊絕緣、金屬填充材料,損耗大;工藝復雜,含深孔刻蝕、金屬填充等精細環節,設備精度要求高,采購及維護成本驚人;良率低,缺陷問題易導致成本增加。

電學性能差:硅材料屬于半導體材料,傳輸線在傳輸信號時,信號與襯底材料有較強的電磁耦合效應,襯底中產生渦流現象,造成信號完整性較差(插損、串擾等)。

相較硅基轉接板,玻璃轉接板有諸多優勢:

一、低成本:受益于大尺寸超薄面板玻璃易于獲取,以及不需要沉積絕緣層,成本大大降低;

二、優良的高頻電學特性:玻璃材料是一種絕緣體材料,介電常數只有硅材料的1/3左右,損耗因子比硅材料低2~3個數量級,使得襯底損耗和寄生效應大大減小,可以有效提高傳輸信號的完整性;

三、大尺寸超薄玻璃襯底易于獲取:康寧、旭硝子以及肖特等玻璃廠商可以量產超大尺寸(大于2m×2m)和超薄(小于50μm)的面板玻璃以及超薄柔性玻璃材料;

四、工藝流程簡單:不需要在襯底表面及TGV內壁沉積絕緣層,且超薄轉接板不需要二次減薄;

五、機械穩定性強:當轉接板厚度小于100μm時,翹曲依然較小。

TGV技術遠期成長空間廣闊

英偉達的H100加速計算卡采用臺積電CoWoS-S 2.5D封裝技術,在硅轉接板上實現7組芯片互連。AMD(超威半導體)MI300采取類似布局,以CoWoS工藝在硅轉接板上封裝6顆GPU、3顆CPU及8組HBM內存。國內方面,壁仞科技BR100系列GPU也采用CoWoS-S封裝,將2顆計算芯粒互連,實現算力的跨越式提升。

CoWoS封裝的核心之一為硅轉接板及TSV工藝,但其存在成本高和電學性能差等不足,而玻璃轉接板及TGV工藝具有低成本、易獲取、高頻電學特性優良等特性,因此,TGV有望作為前者替代品,成為先進封裝核心演進方向之一,疊加AI浪潮之下加速計算芯片需求高增,TGV遠期成長空間廣闊。其實,不止可用于轉接板,搭配TGV技術,玻璃基板在光電系統集成領域、MEMS封裝等領域也有巨大的應用前景,可以作為IC載板使用,以在部分領域替代現在主流的有機載板。

參考來源:

鐘毅.芯片三維互連技術及異質集成研究進展

陳俊偉.玻璃在5G通訊中的應用

東方證券《先進封裝持續演進,玻璃基板大有可為》

(中國粉體網編輯整理/月明)

注:圖片非商業用途,存在侵權告知刪除!